作者: 深圳市昂洋科技有限公司發(fā)表時間:2025-10-24 14:01:24瀏覽量:12【小中大】

三環(huán)電容(尤其是X7R材質(zhì)MLCC)在電源去耦優(yōu)化中,需結(jié)合其容量-電壓特性、封裝尺寸及頻率響應特性進行選型與布局,核心原則是通過多容量組合覆蓋寬頻噪聲,并優(yōu)化寄生參數(shù)以降低電源阻抗。以下是具體分析:

一、三環(huán)電容容量-電壓特性對去耦的影響

電壓系數(shù)與容量衰減

X7R電介質(zhì)電容的容量隨電壓升高而衰減,例如三環(huán)TCC0603X7R104K500CT(100nF/50V)在額定電壓下容量可能衰減5%-10%。優(yōu)化建議:

工作電壓降額至額定值的70%以下(如35V),可減少容量衰減至3%以內(nèi),提升高頻去耦穩(wěn)定性。

對電壓敏感電路(如ADC參考電壓),優(yōu)先選擇C0G材質(zhì)電容(容量穩(wěn)定性±1%),但需注意其容量上限較低(通常≤0.1μF)。

容量與自諧振頻率的關(guān)系

三環(huán)MLCC的自諧振頻率(SRF)與容量成反比,例如:

0.1μF(0603封裝)SRF≈15MHz,適用于10MHz以下噪聲抑制;

10nF(0402封裝)SRF≈100MHz,可覆蓋100MHz以下高頻噪聲。

優(yōu)化建議:

采用“大容量+小容量”組合,如10μF鉭電容(低頻)+0.1μF MLCC(中頻)+10nF MLCC(高頻),形成寬頻覆蓋。

避免單一容量電容,防止特定頻段噪聲漏濾。

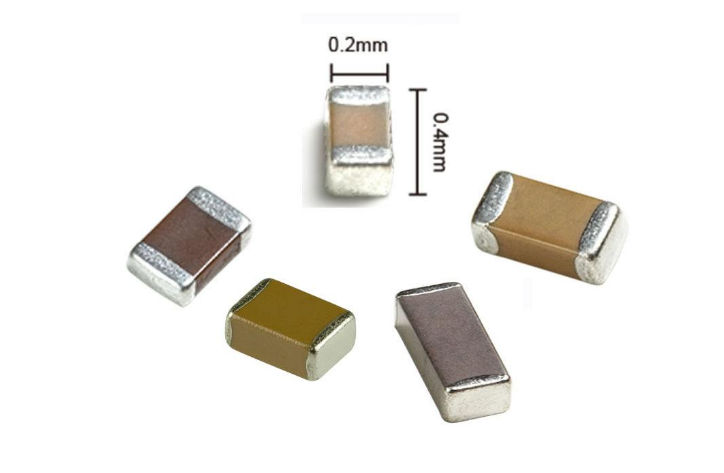

二、封裝尺寸與寄生參數(shù)優(yōu)化

封裝對等效串聯(lián)電感(ESL)的影響

三環(huán)MLCC的ESL隨封裝尺寸減小而降低,例如:

0603封裝ESL≈3nH,0402封裝ESL≈1.5nH,0201封裝ESL≈0.8nH。

優(yōu)化建議:

高頻去耦(>10MHz)優(yōu)先選擇0402或0201封裝,減少寄生電感對高頻噪聲的抑制效果。

低頻去耦(<1MHz)可使用0603或0805封裝,平衡成本與性能。

布局對電源阻抗的影響

去耦電容需貼近芯片電源引腳放置,以減少走線電感。例如:

若0.1μF電容距離芯片引腳5mm,走線電感≈5nH,在100MHz下阻抗≈3.14Ω,可能抵消電容的低阻抗特性。

優(yōu)化建議:

采用“就近放置”原則,將小容量高頻電容(如0.1μF)直接放置在芯片電源引腳旁,通過短走線或過孔連接至地平面。

大容量低頻電容(如10μF)可放置在電源入口附近,作為電荷儲備庫。

三、三環(huán)電容在電源去耦中的典型應用

數(shù)字電路去耦

場景:高速微處理器(如ARM Cortex-M系列)電源去耦。

方案:

并聯(lián)1個10μF鉭電容(抑制低頻噪聲)和1個0.1μF MLCC(抑制高頻噪聲)。

三環(huán)TCC0603X7R104K500CT(0.1μF/50V)作為高頻去耦主力,配合鉭電容實現(xiàn)寬頻覆蓋。

效果:電源阻抗在1kHz-100MHz范圍內(nèi)≤0.1Ω,滿足數(shù)字電路對電源穩(wěn)定性的要求。

模擬電路去耦

場景:高精度ADC參考電壓去耦。

方案:

使用三環(huán)TCC0603C0G1R0B500CT(10pF/50V,C0G材質(zhì))作為高頻去耦,避免X7R電容的電壓系數(shù)導致容量波動。

配合1μF薄膜電容(低ESR)抑制低頻噪聲。

效果:電源紋波抑制比(PSRR)在1MHz下≥60dB,確保ADC參考電壓穩(wěn)定性。