作者: 深圳市昂洋科技有限公司發表時間:2025-10-21 14:24:45瀏覽量:7【小中大】

太誘薄膜電感在高頻下出現寄生電容問題,主要是由其物理結構和工作原理導致,這些寄生電容在高頻時等效值增大,會對電路性能產生顯著干擾,可通過以下方法解決:

優化電感器設計

優化線圈繞制方式:通過減少線圈層數、增大線圈間距等方法,可以有效降低寄生電容。例如,采用分段繞組、交錯繞組等方式,能夠減少線圈之間的互容,從而降低寄生電容。

選擇合適的磁芯材料和形狀:采用高電阻率、低介電常數的材料作為電感器的磁芯和繞組,可以降低寄生電容。不同的磁芯材料具有不同的介電特性,選擇合適的材料有助于減少寄生電容的產生。

選用合適的材料和結構

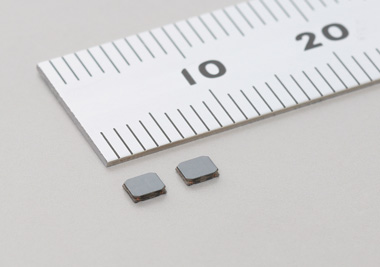

采用高性能電感器:市面上有一些專門設計的低寄生電容電感器可供選擇,這些電感器通常采用特殊的材料和結構設計,如薄膜電感采用薄膜沉積技術和精密光刻工藝制造,其線圈間距極小,有效降低了寄生電容,在高頻(GHz范圍)下具有高自諧振頻率和高品質因數(Q值)。

優化電感器結構:除了上述提到的繞組方式優化外,還可以從整體結構上進行改進。例如,采用屏蔽式結構,將電感器內部線圈與外部電路進行隔離,減少外部電磁場對電感器的影響,同時也能降低電感器產生的電磁場對其他電路的干擾,從而間接減少寄生電容的影響。

采用屏蔽技術

避免電磁耦合:避免將電感器放置在高頻信號線附近,以減少電磁耦合。高頻信號線產生的電磁場可能會在電感器上感應出電荷,形成寄生電容。因此,在電路布局時,應合理規劃電感器和信號線的位置,保持一定的距離。

優化走線方式:盡量減少線路長度和彎折,以降低線路間的寄生電容。長距離的走線和過多的彎折會增加線路之間的互容,從而增大寄生電容。在PCB設計中,可以采用直線走線、45度角走線等方式,減少線路的彎折。